冯·诺依曼结构

冯·诺伊曼结构与 存储程序型计算机 是互相通用的名词

哈佛结构 是一种将程序数据与普通数据分开存储的设计概念,可以说是冯·诺依曼结构的一种。

存储程序计算机在体系结构上主要特点有:

- 以运算单元为中心

- 采用存储程序原理

- 存储器是按地址访问、线性编址的空间

- 控制流由指令流产生

- 指令由 操作码 和 地址码 组成

- 数据以二进制编码

五个组成部分:

- 存储器

- 控制器

- 运算器(算术逻辑单元)

- 输入

- 输出

历史

冯·诺依曼由于在曼哈顿工程中需要大量的运算,从而使用了当时最先进的两台计算机 Mark I 和 ENIAC,在使用 Mark I 和 ENIAC 的过程中,他意识到了存储程序的重要性,从而提出了存储程序逻辑架构。

最早的计算机内含固定用途的程序,并非可编程,若想要改变此机器的程序,你必须更改线路、更改结构甚至重新设计机器。而存储程序型计算机的概念改变了这一切。借着将指令当成一种特别类型的静态数据,一台存储程序型计算机可轻易改变其程序,并在程序控制下改变其运算内容。

优势

冯·诺依曼架构第一次 将存储器和运算器分开,指令和数据均放置于存储器中,为计算机的 通用性 奠定了基础。虽然在规范中计算单元依然是核心,但冯·诺依曼架构事实上导致了 以存储器为核心 的现代计算机的诞生。

注:请各位在心里明确一件事情:存储器指的是内存,即 RAM。磁盘理论上属于输入输出设备。

缺陷

- 程序可修改很可能是非常具伤害性的:在一个简单的存储程序型计算机上,一个设计不良的程序可能会伤害自己、其他程序甚或是操作系统,导致死机、缓存溢出就是一个典型例子。而创造或更改其他程序的能力也导致了恶意软件的出现。利用缓存溢出,一个恶意程序可以覆盖调用堆栈(Call stack)并改写代码,并且修改其他程序文件以造成连锁破坏。存储器保护机制及其他形式的访问控制可以保护意外或恶意的代码更动。

- 冯·诺伊曼瓶颈(von Neumann bottleneck):在内存容量指数级提升以后,CPU 和内存之间的数据传输带宽成为了瓶颈。缓解的办法有:

- 在 CPU 和内存之间提供 cache(缓存,速度比内存快很多倍)

- 将数据和指令分开存储并能够做到同时访问(在一般的冯·诺依曼结构中数据和指令放在同一内存通过同一数据总线访问,取数据和取指令不能同时进行,而哈佛结构则是将数据和指令分开,可同时访问)

- 分支预测和流水线

实际上,绝大多数现代计算机使用的是所谓的“Modified Harvard Architecture”,指令和数据共享同一个 address space,但缓存是分开的。在内存里,指令和数据是在一起的。而在 CPU 内的缓存中,还是会区分指令缓存和数据缓存,最终执行的时候,指令和数据是从两个不同的地方出来的。你可以理解为在 CPU 外部,采用的是冯诺依曼模型,而在 CPU 内部用的是哈佛结构。

大部分的DSP都没有缓存,因而直接就是哈佛结构。

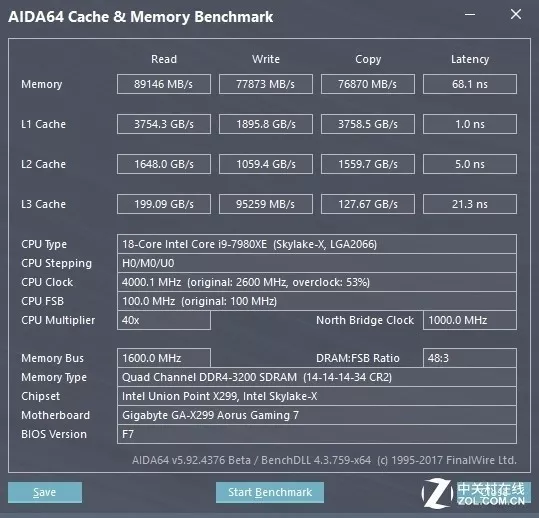

上图是 i9-7980XE 18 核 36 线程的民用最强 CPU,其配合超频过的 DDR4 3200MHz 的内存,测试出的内存读取速度为 90GB/S。看起来很快了是不是?看看图中的 L1 Cache,3.7TB/S。

我们再来算算时间。这颗 CPU 最大睿频 4.4GHz,就是说 CPU 执行一个指令需要的时间是 0.000000000227273 秒,即 0.22ns(纳秒),而内存的延迟是 68.1ns。换句话说,只要去内存里取一个字节,就需要 CPU 等待 300 个周期,何其的浪费 CPU 的时间啊。

CPU L1 L2 L3 三级缓存是使用和 CPU 同样的 14 纳米工艺制造的硅半导体,每一个 bit 都使用六个场效应管(通俗解释成三极管)构成,成本高昂且非常占用 CPU 核心面积,故不能做成很大容量。

除此之外,L1 L2 L3 三级缓存对计算机速度的提升来源于计算机内存的「局部性」,相关内容我们之后会专门讨论。

RAM(Random Access Memory,俗称 内存):内存最大的特点是:掉电失去数据。程序是静态的文件存放在外存中,进程正在运行的程序,进程存放在内存中。我们之所以使用内存是因为内存的速度比外存快 100 倍左右。

ROM(Read-Only Memory,只读存储器):ROM 掉电不失去数据。